1 多層堆疊技術(shù)

2. 5D 封裝和 3D 封裝是兩種常用的晶圓級多層堆疊技術(shù)。2. 5D 封裝是將芯片封裝到 Si 中介層上,并利用 Si 中介層上的高密度走線進行互連。由于 Si 中介層上沒有有源器件,所以這種技術(shù)是通過 Si 中介層使多顆芯片在同一平面上互連,沒有形成芯片之間的三維堆疊,因此被稱為 2. 5D 封裝。目前 2. 5D 封裝的代表性技術(shù)是臺積電的基底上 晶 圓 上 芯 片 ( chip-on-wafer-on-substrate,CoWoS) 封裝和英特爾的嵌入式多芯片互連橋接( embedded multi-die interconnect bridge, EMIB )封裝。

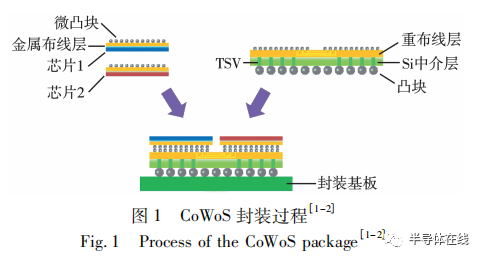

CoWoS 封裝的過程如下: 首先,制備好需要進行封裝的芯片,芯片的正面有微凸塊,背面磨薄,將已知良品芯片 ( known good die,KGD) 切割待用,無需封裝; 之后,在一片裸晶圓上進行TSV、重布線層及微凸塊的布局,將晶圓背面減薄并制作好凸塊,制成無源 Si 中介層; 然后將 KGD倒裝、對準(zhǔn),與 Si 中介層面對面鍵合,再將整體通過凸塊與封裝基板相連。CoWoS 封裝的具體過程如圖 1 所示。

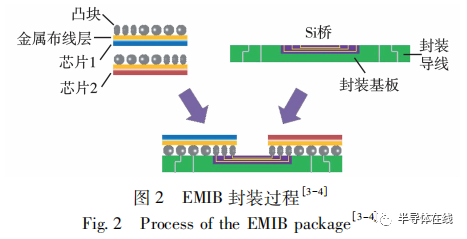

EMIB 封裝是在封裝基板中嵌入一小塊 Si 橋作為多片芯片的互連結(jié)構(gòu)。與臺積電的 CoWoS封裝類似,首先仍是制備好需要進行封裝的芯片,芯片背面磨薄,但正面有與封裝基板相連的凸塊,KGD 切割待用,無需封裝。同時,EMIB 封裝無需Si 中介層,而是直接在封裝基板中嵌入具有互連功能的 Si 橋。然后將 KGD 倒裝、對準(zhǔn),直接與嵌有 Si 橋的封裝基板通過凸塊相連。EMIB 封裝的具體過程如圖 2 所示。與臺積電的 CoWoS 封裝相比,EMIB 封裝既不需要 TSV 工藝,也不需要 Si 中介層,因此其具有封裝良率高、設(shè)計簡單、成本更低等優(yōu)點。

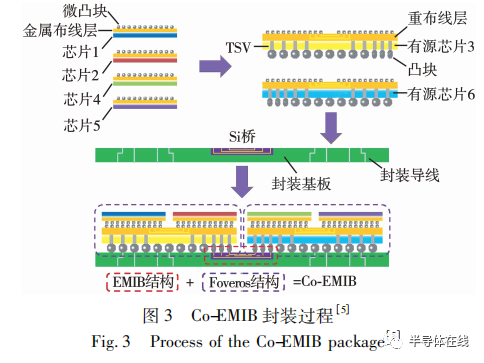

與 2. 5D 封裝技術(shù)不同,3D 封裝則真正做到了芯片之間的垂直互連。下面將對英特爾推出的兩種 3D 封裝技術(shù)進行簡要介紹,即用于邏輯芯片堆疊的 Foveros 技術(shù)以及由 EMIB 和 Foveros 封裝技術(shù)結(jié)合而成的 Co-EMIB 技術(shù)。

Foveros 的封裝過程與 CoWoS 較為類似,不同之處在于 CoWoS 的中介層是一片裸晶圓,因此它是無源中介層,但是 Foveros 的中介層是具有功能的芯片,屬于有源 Si 中介層。

Co-EMIB 則是英特爾綜合了 EMIB 和 Foveros兩種封裝技術(shù)而實現(xiàn)的創(chuàng)新封裝技術(shù),在 Foveros技術(shù)的水平物理層互連和垂直互連的同時,借由EMIB 封裝實現(xiàn) Foveros 3D 堆疊之間的水平互連,復(fù)雜的互連結(jié)構(gòu)對布線設(shè)計水平提出了極高的要求。Co-EMIB 的封裝過程是先利用 Foveros 的方法,將多塊芯片形成不同的組塊,再利用 EMIB 封裝的方法將這些組塊通過 Si 橋連接起來。不管是 2D 水平互連還是 3D 堆疊互連,單片與單片之間都可以實現(xiàn)近乎 SOC 級高度整合的低功耗、高帶寬、高性能表現(xiàn),為芯片封裝帶來絕佳的靈活性。Co-EMIB 封裝的具體過程如圖 3 所示。

從以上介紹可以看出,TSV 工藝和晶圓鍵合與解鍵合工藝是晶圓級多層堆疊技術(shù)的兩項關(guān)鍵工藝。基于此,本文將對這兩項關(guān)鍵工藝及晶圓級多層堆疊的可靠性管理進行詳細(xì)介紹,為集成電路產(chǎn)業(yè)的發(fā)展提供一定的思路。

2 TSV關(guān)鍵工藝

TSV 是一種穿通 Si 晶圓或芯片的垂直互連結(jié)構(gòu),可以完成連通上下層晶圓或芯片的功能,是晶圓級多層堆疊技術(shù)中有效提高系統(tǒng)整合度與效能的關(guān)鍵工藝。

TSV 工藝依據(jù)制程的先后可以分為先通孔、中通孔和后通孔 3 種技術(shù)方案。先通孔是指在沒有進行任何 CMOS 工藝前,先在空白 Si 片上制作通孔。在該方案中,由于通孔需要經(jīng)歷后續(xù)所有CMOS 制造步驟,因此通孔的填充材料必須要能經(jīng)受住高于1 000 ℃的全部熱加工工藝。因此,在先通孔方案中,最常用的填充材料是多晶硅。先通孔方案的優(yōu)點是不需要種子層,且絕緣層可以采用傳統(tǒng)的氧化工藝制作。

中通孔是指在 CMOS 器件即將完成和晶圓減薄工藝前進行 TSV 的制作,一般是在器件結(jié)構(gòu)基本完成而全局互連尚未實現(xiàn)的階段進行。該方案的優(yōu)點是在制作通孔時,CMOS 結(jié)構(gòu)已經(jīng)完成并鈍化,此時,Si 片不會再經(jīng)歷高溫工藝,因此可以使用電性能和熱性能比多晶硅更優(yōu)良的 Cu 作為通孔填充材料。

后通孔是指在晶圓減薄后再進行 TSV 的制作。在該方案中,晶圓在通孔形成前已經(jīng)減薄到其最終厚度,刻蝕 TSV 后不便進行 Cu 的填充,因此后通孔方案是將 Si 片固定在載片或者底部晶圓上,進行減薄后,再進行 TSV 的刻蝕和填充。

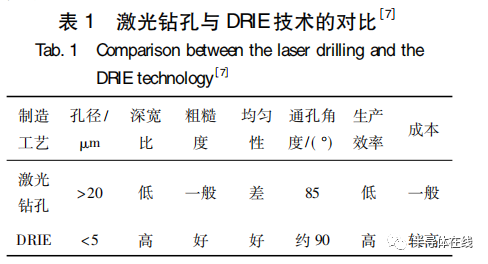

由于 Cu 的熱膨脹系數(shù)遠大于 Si,因此通孔中填充過多的 Cu 容易導(dǎo)致可靠性問題。為了提高通孔可靠性,通孔的直徑越小越好,所以生成小孔徑高深寬比 TSV 的 DRIE 成為 TSV 制作技術(shù)的唯一選擇。

2. 1 通孔的形成

晶圓上的 TSV 形成是 TSV 技術(shù)的核心,目前的通孔加工技術(shù)主要分為兩種: 一種是激光鉆孔;另一 種 是 深 反 應(yīng) 離 子 刻 蝕 ( deep reactive ionetching,DRIE) 。表 1 列出了兩種不同通孔制作技術(shù)的對比。

激光鉆孔技術(shù)是利用激光的定向性和高功率密度使晶圓表面迅速被加熱至氣化溫度,蒸發(fā)形成孔洞。由于激光本身的性質(zhì)無法滿足小孔徑、高深寬比的 TSV 制作,因此激光鉆孔技術(shù)無法用于2. 5D/3D 封裝技術(shù)。

DRIE 技術(shù)是將聚合物鈍化層的沉積和對單晶硅的刻蝕這兩種工藝過程組合在一起循環(huán)交替進行,這樣可以避免沉積和刻蝕之間相互影響,保證了鈍化層的穩(wěn)定可靠,從而形成側(cè)壁陡直的高深寬比扇貝結(jié)構(gòu)。最典型的深反應(yīng)離子刻蝕方法是被稱為 “Bosch”工藝的方法,采用 SF6和 C4 F8在常溫下實現(xiàn)對 Si 的刻蝕。SF6為刻蝕氣體,用于對溝槽側(cè)壁和底部的刻蝕, C4 F8為保護氣體,通過在側(cè)壁表面生長一層 ( CF2 ) n有機聚合物保護膜,實現(xiàn)對已刻蝕側(cè)壁的保護。具體過程是,先用 SF6刻蝕Si 表面,然后在側(cè)壁上沉積一層( CF2 ) n高分子鈍化膜,再通入 SF6刻蝕掉鈍化膜,接著進行 Si 基材的刻蝕,如此反復(fù),從而形成一個局部的各向異性刻蝕。

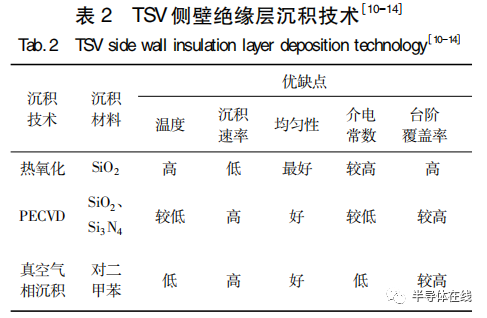

2. 2 絕緣層的沉積

在填充金屬之前,必須先進行絕緣層的沉積,隔斷填充金屬與 Si 之間的電導(dǎo)通。通孔內(nèi)壁絕緣層材料包括硅氧化物、硅氮化物和聚合物等。不同絕緣層材料需要用不同的沉積技術(shù),如表 2 所示。等離子體增強化學(xué)氣相沉積 ( PECVD)技術(shù)的沉積速率高、工藝溫度低、均勻性好且臺階覆蓋率高,廣泛應(yīng)用于沉積 SiO2等絕緣層材料。真空氣相沉積聚對二甲苯的工藝溫度最低,在要求更低沉積溫度的 TSV 工藝中應(yīng)用也比較廣泛。

2. 3 阻擋層和種子層的沉積

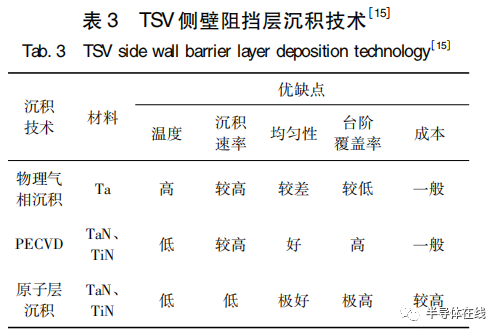

由于 Cu 具有優(yōu)秀的電性能和熱性能,且成本低廉,目前 TSV 大多采用 Cu 來填充。但 Cu 作為填充材料有以下缺點: ①Cu 在 SiO2介質(zhì)中的擴散速度很快,易使其介電性能嚴(yán)重退化; ②Cu 對半導(dǎo)體載流子具有很強的陷阱效應(yīng),擴散后將嚴(yán)重影響半導(dǎo)體器件的電性特征; ③Cu 和 SiO2的黏附強度較差,容易對器件的可靠性產(chǎn)生影響。因此,在Cu 和半導(dǎo)體本體之間需要沉積一層阻擋層,既能阻擋 Cu 向 SiO2中擴散,也能提高 Cu 在 SiO2表面的黏附強度。通常的阻擋層材料包括 Ta、TaN/Ta、TiN 等金屬或金屬化合物。常見阻擋層材料及其沉積方法如表 3 所示。

在阻擋層之后還會再生長一層種子層,其作用有二: 一是生產(chǎn)中一般采用電鍍的方式來生長 Cu,電鍍時需要導(dǎo)電,因此在阻擋層表面覆蓋一層 Cu種子層用以導(dǎo)電,通電后,電鍍液中的 Cu 離子與電子結(jié)合形成鍍在種子層表面的 Cu; 二是種子層可以提供 Cu 晶核,晶核越多,結(jié)晶越均勻,避免晶粒異常長大。

2. 4 TSV的填充

Cu 的電阻率僅為 1. 75×10-8Ω·m,是良好的導(dǎo)電材料,加之其價格低廉,因此成為 TSV 填充材料的首選。TSV 的 Cu 填充技術(shù)主要有電鍍、磁控濺射、化學(xué)氣相沉積、原子層沉積等方法。由于電鍍的成本更低且沉積速率更快,工業(yè)上一般采用電鍍 Cu 工藝來填充 TSV。

電鍍 Cu 的填充效果與 TSV 的直徑有關(guān),當(dāng)TSV 的直徑在 25 μm 以上時,Cu 的填充效果較好,但由于 Cu 的熱膨脹系數(shù)與 Si 材料不匹配,過多的Cu 填充可能會導(dǎo)致出現(xiàn)可靠性問題,因此需要盡量減小 TSV 的尺寸。然而當(dāng)孔徑小于10 μm后,對于小孔徑、高深寬比的 TSV,底部未完成填充時,上層的開口可能已經(jīng)封閉,就會形成電鍍空洞,因此均勻電鍍銅工藝不適用于小孔徑 TSV 的填充。

為實現(xiàn)無空洞電鍍 Cu,開發(fā)了一種 “自底向上”的電鍍工藝。這種工藝通常利用特殊的電鍍促進劑和抑制劑來加速通孔內(nèi)部的沉積速率和抑制通孔外表面的沉積速率,通過調(diào)整促進劑和抑制劑的比例,使二者相互平衡,從而防止電鍍空洞的產(chǎn)生。

2. 5 晶圓表面的平坦化

完成電鍍 Cu 后,晶圓的表面沉積了一層較厚的不均勻 Cu 層,一般采用 CMP 技術(shù)將多余的 Cu去除并將晶圓表面平坦化。Cu 的研磨工藝一般分為三步: 第一步用較快的研磨速率去除晶圓表面大部分的 Cu; 第二步通過降低研磨速率研磨掉與阻擋層接觸的 Cu,使研磨停留在阻擋層上; 第三步研磨掉阻擋層和少量的氧化硅。其中第三步是Cu 的 CMP 工藝的難點,磨得太少可能形成碟形缺陷,磨得太多容易導(dǎo)致侵蝕,因此第三步的時間控制是 Cu CMP 工藝的重點。

2. 6 晶圓的減薄

在先通孔和中通孔工藝中,晶圓表面平坦化后,還需要進行晶圓背面的減薄使 TSV 露出,而在后通孔工藝中,晶圓在進行 Bosch 刻蝕工藝前就會進行減薄。晶圓減薄的目的是使 TSV 露出,在晶圓級多層堆疊技術(shù)中,需要將多片晶圓進行堆疊鍵合,同時總厚度還必須滿足封裝設(shè)備的要求,因此目前 0. 3~0. 4 mm 的晶圓厚度必須經(jīng)過減薄才能滿足要求。目前較為先進的多層堆疊使用的芯片厚度均在 100 μm 以下。未來如果需要疊加更多層,芯片的厚度需減薄至 25 μm 甚至更小。傳統(tǒng)的晶圓減 薄 技 術(shù) 包 括 機 械 磨 削、CMP 和 濕 法 腐 蝕等。對于晶圓級多層堆疊來說,單一的晶圓減薄技術(shù)無法滿足工藝要求,需采用復(fù)合方法進行晶圓的減薄,一般是先利用機械磨削將晶圓減薄到一定程度后,再利用 CMP 和濕法腐蝕等減薄工藝進一步減薄至目標(biāo)厚度。

晶圓經(jīng)過減薄后通常容易產(chǎn)生變形或翹曲,給之后的工序帶來困難。目前業(yè)界主流的解決方案是采用一體機的思路,將晶圓的磨削、拋光、保護膜去除和劃片膜粘貼等工序集合在一臺設(shè)備內(nèi)。晶圓從始至終都被吸在真空吸盤上,始終保持平整狀態(tài),從而防止了晶圓在工序間搬運時產(chǎn)生變形或翹曲。

3 晶圓鍵合與解鍵合關(guān)鍵工藝

晶圓鍵合與解鍵合工藝也是多層晶圓堆疊技術(shù)的關(guān)鍵工藝之一,用于完成兩片器件晶圓的 “面對面”堆疊,或利用載片晶圓實現(xiàn)多片器件晶圓的 “背對面”堆疊。

根據(jù)鍵合材料的不同,晶圓的鍵合主要分為Si-Si 直 接 鍵 合、金 屬 熱 壓 鍵 合、共 晶 鍵合和聚合物鍵合等鍵合方法。根據(jù)鍵合的性質(zhì),分為永久鍵合與臨時鍵合。其中,Si-Si 直接鍵合對工藝的要求較高,但鍵合過程較為簡單,鍵合強度大; 金屬熱壓鍵合和共晶鍵合主要用于芯片或晶圓的金屬鍵合環(huán)之間的鍵合; 聚合物鍵合熱穩(wěn)定性較差,不常用于器件晶圓之間的鍵合,但可以利用這一特點用于器件晶圓與載片晶圓之間的臨時鍵合,以方便其解鍵合過程。目前這 4 種鍵合方法,以及綜合多種鍵合技術(shù)形成的混合鍵合法在工業(yè)上均得到了廣泛使用。

對于兩片晶圓之間的鍵合,目前主流的方法有3 種: Si-Si 永久鍵合、聚合物臨時鍵合和 Si-Si 直接鍵合與金屬熱壓鍵合的混合鍵合。

Si-Si 永久鍵合采用的載片晶圓材料為 Si 片。將器件晶圓和載片晶圓的正面拋光并用表面活性劑處理,將器件晶圓倒裝與載片晶圓貼合,在室溫下進行預(yù)鍵合。經(jīng)過拋光處理的 Si 或 SiO2表面會產(chǎn)生一些懸掛的 Si—O 鍵,這些 Si—O 鍵中的 O 原子處于不穩(wěn)定的狀態(tài),會從表面活性劑中吸附 H+離子形成羥基。兩片晶圓貼近后,一片晶圓上羥基中的 O 原子可以和另一片晶圓上羥基中的 H 原子形成氫鍵,使兩片晶圓緊密貼合。之后,對兩片晶圓進行高溫退火處理,兩晶圓表面的羥基會發(fā)生聚合反應(yīng),脫去一個 H2O 分子,于是兩邊的 Si 通過與O 形成堅固的 Si—O 鍵而鍵合在一起。

由于兩片晶圓是通過范德華力預(yù)鍵合的,因此對表面平整度、清潔度的要求也較高; 而兩片晶圓的鍵合層是沒有明確界面的硅氧化物,因此這種鍵合是永久性的,鍵合強度很高,載片晶圓的解鍵合只能通過完全磨削實現(xiàn),所以 Si-Si 永久鍵合步驟較為簡單,但載片消耗量大,成本相對較高。

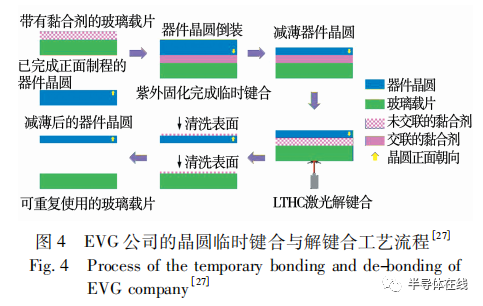

聚合物臨時鍵合采用的載片晶圓材料為玻璃。奧地利的公司提供了一種聚合物臨時鍵合的方案。在該方案中,采用紫外固化液態(tài)黏合劑將器件晶圓和玻璃載片進行臨時鍵合。如圖 4所示,經(jīng)過背面磨削后,利用光熱轉(zhuǎn)換 ( light to heat conversion,LTHC) 激光進行解鍵合,然后清洗表面,將黏合劑從晶圓上除去,完成整個工藝流程。

EVG 公司采用的 UV 固化液態(tài)黏合劑是一種特殊的聚合物材料,可以在紫外光的照射下發(fā)生化學(xué)反應(yīng),聚合物會產(chǎn)生交聯(lián)從而實現(xiàn)晶圓鍵合。聚合物臨時鍵合法采用黏合劑將兩片晶圓進行鍵合,因此對晶圓表面平整度、清潔度要求不高。雖然這種方法的鍵合強度較低、對熱不穩(wěn)定,但也使解鍵合工藝容易實現(xiàn)。清洗后的玻璃載片可以重復(fù)使用,有效地降低了鍵合成本。

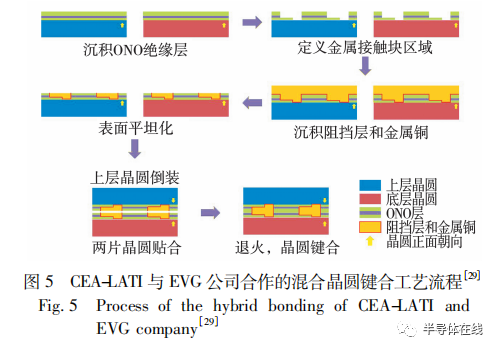

混合鍵合主要用于兩片器件晶圓的鍵合,而非器件晶圓與載片晶圓的鍵合。法國原子能委員會電子與信息技術(shù)實驗室 ( CEA-LATI) 與 EVG 公司合作,于 2017 年 率 先 實 現(xiàn) 12 英 寸 ( 1 英 寸 =2. 54 cm) 晶圓的混合鍵合,其混合鍵合中的金屬接觸 塊 的 材 料 是 Cu,金 屬 接 觸 塊 的 間 隔 約 為1 μm。混合鍵合的工藝流程如圖 5所示。首先,在兩片晶圓上沉積硅氧化物-硅氮化物-硅氧化物 ( ONO) 絕緣層,然后用大馬士革工藝定義金屬接觸塊區(qū)域,沉積 TaN/Ta 阻擋層并沉積 Cu,再進行特殊的表面處理使表面粗糙度小于 0. 5 nm,最后,將一片晶圓倒裝與另一片晶圓貼合,在400 ℃下退火,使兩片晶圓形成鍵合。混合鍵合不需要載片晶圓或黏合劑,同時不需要 TSV 即可使兩片器件晶圓鍵合,具有成本低廉、工藝簡單等優(yōu)點。

4 晶圓級多層堆疊技術(shù)的可靠性管理

集成電路可靠性的定義是系統(tǒng)或元器件在規(guī)定的條件下和規(guī)定的時間內(nèi)完成規(guī)定功能的能力。可靠性測試從集成電路誕生開始,就一直是芯片設(shè)計、制造的研究開發(fā)中的一個重要部分。當(dāng)芯片進入多層堆疊時代后,多層芯片的垂直異構(gòu)堆疊互連結(jié)構(gòu)也對芯片可靠性的保障和提高帶來了巨大的挑戰(zhàn)。

4. 1 2. 5D/3D 封裝中的力學(xué)管理

在 2. 5D/3D 封裝中,力學(xué)特性引起的可靠性問題主要分為兩個方面: 一是 TSV 中填充的 Cu與 Si 之間的熱膨脹系數(shù)不同,因此在 TSV 結(jié)構(gòu)受熱或遇冷時可能導(dǎo)致 Cu 與 Si 之間的界面發(fā)生分層失效; 二是在晶圓減薄的過程中,如果使用不適當(dāng)?shù)墓に噮?shù),可能會導(dǎo)致減薄過程中產(chǎn)生較大的磨削應(yīng)力導(dǎo)致晶圓碎片,也可能導(dǎo)致在磨削后晶圓表面殘余應(yīng)力增加,產(chǎn)生晶圓翹曲,不利于后續(xù)工藝的開展。因此,需針對這兩方面進行力學(xué)的可靠性管理。

對于 TSV 而言,由于其中的黏附層比絕緣層薄很多,以下分析忽略黏附層產(chǎn)生的形變。Si、SiO2和 Cu 的熱膨脹系數(shù)分別約為3×10-6、6×10-7和 1. 8×10-5℃ -1,當(dāng)溫度變化時,Cu 的形變量大約是 Si 的 6 倍,是 SiO2的 30 倍。因此,在溫度變化時,受力最強的點是通孔表面 Cu 與 SiO2的接觸點,可以將這個點的受力作為判斷 Cu 是否會發(fā)生分層和開裂的指標(biāo)。以升溫為例,當(dāng)孔徑較小時,若 TSV 越深,受熱后 Cu 膨脹的量就越多,因此通孔表面 Cu 與 SiO2的接觸點受到的應(yīng)力越大。實驗表明,對于無缺陷的 TSV 結(jié)構(gòu),Cu 與 SiO2的界面附近單元中的應(yīng)變較小,不足以導(dǎo)致分層和開裂。因此,對于受應(yīng)力影響比較大的小孔徑 TSV,應(yīng)盡量避免工藝制程中可能出現(xiàn)的如表面粗糙等可以導(dǎo)致應(yīng)力集中的缺陷。

在晶圓減薄的過程中,晶圓表面由于砂輪的磨削會產(chǎn)生晶格缺陷,這些晶格缺陷會導(dǎo)致殘余應(yīng)力在晶圓表面產(chǎn)生。當(dāng)晶圓厚度大于 100 μm 時,殘余的應(yīng)力還不足以導(dǎo)致晶圓翹曲。但當(dāng)晶圓減薄到 100 μm 以下時,在殘余應(yīng)力的影響下,晶圓會發(fā)生明顯的形變。而在進行晶圓減薄時,減小砂輪磨削的轉(zhuǎn)速可以加速殘余應(yīng)力的釋放,因此可以減小晶圓翹曲的程度。然而過小的轉(zhuǎn)速會導(dǎo)致晶圓減薄效率的降低,因此可以將減薄過程分成兩個步驟,首先將晶圓快速磨削至100 μm左右,再采用較小的磨削速率將晶圓減薄至目標(biāo)厚度,這樣可以盡量避免晶圓由于殘余應(yīng)力發(fā)生過大的形變。

4. 2 2. 5D/3D 封裝中的熱學(xué)管理

熱學(xué)管理是 2. 5D/3D 封裝中的重要問題之一,其原因在于: ①多功能芯片的堆疊使單位面積上的總功耗增大,產(chǎn)生的熱量增高,且無有效的散熱通道; ②晶圓減薄后會導(dǎo)致芯片發(fā)生熱量聚集,產(chǎn)生過熱點。2. 5D/3D 封裝的散熱可以從封裝級熱設(shè)計和外部散熱措施兩方面來考慮。封裝級熱設(shè)計包括優(yōu)化封裝結(jié)構(gòu)和應(yīng)用封裝級冷卻技術(shù),例如加裝銅散熱板、鋁封裝蓋等。外部散熱措施包括空氣冷卻、液體冷卻和相變冷卻等方式。液體冷卻和相變冷卻的效率較高,但需要加裝附加設(shè)備,增加了系統(tǒng)的體積和復(fù)雜性,也提高了制造和維護的成本,而空氣冷卻由于其低成本、易維護和高可靠性的特點成為目前較為常用的 2. 5D/3D 封裝的熱學(xué)管理方式。

描述封裝熱性能的指標(biāo)是結(jié)點至環(huán)境的熱阻,熱阻越高代表越難散熱,封裝的熱性能越差。顯然,Cu 的熱阻比 Si 和 SiO2的更小,而空氣的熱阻是最大的。因此,增加 TSV 的數(shù)量、增大 TSV 的孔徑或減少填充 Cu 時產(chǎn)生的空氣空洞都可以減小芯片或晶圓的平均熱阻。而從厚度方面考慮,芯片或晶圓越薄,其最大結(jié)溫和熱阻越高,熱點也就越集中,因此增加 Si 中介層的厚度可以有效提高整體的熱性能。對于芯片的堆疊而言,堆疊芯片的數(shù)目越多,整體的最大結(jié)溫越高,因此堆疊芯片的數(shù)目受到允許結(jié)溫的限制,盡量采取交錯排布熱源的方式進行芯片堆疊,若熱源必須重疊布置,可適當(dāng)增加多個重疊熱源之間的距離,但不能過于靠近芯片邊緣。

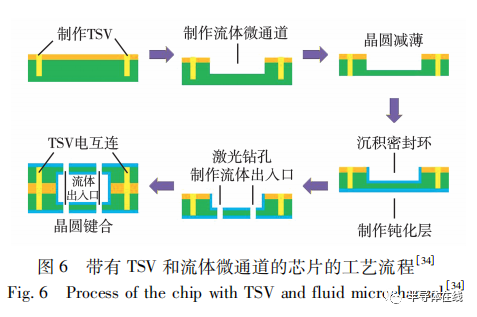

外部散熱措施會增加系統(tǒng)的復(fù)雜性,但是可以極大地提高系統(tǒng)的散熱能力。目前工業(yè)上采取的方法是在芯片或晶圓上增加熱管理微通道,可以使流體在微通道中流通,提高散熱效率。并在流體通道周圍設(shè)置密封環(huán),將流體與電互連隔絕開來。具體的工藝流程如圖 6所示。在刻蝕 TSV 通孔后,會刻蝕出比 TSV 淺的流體微通道,晶圓減薄后,TSV 中的金屬會露出,但流體微通道仍保持密閉。

4. 3 2. 5D/3D 封裝中的電磁學(xué)管理

2. 5D/3D 封裝作為一種異質(zhì)集成封裝,內(nèi)部包含有半導(dǎo)體材料、絕緣材料、金屬材料、合金材料等各種異質(zhì)材料,導(dǎo)致系統(tǒng)內(nèi)部的電磁環(huán)境比較惡劣。同時,不同的芯粒封裝在一起,產(chǎn)生了多種輻射源,各輻射源的外部輻射相互疊加,可使系統(tǒng)總體輻射強度增強,對外部電路產(chǎn)生電磁干擾。因此,“封裝內(nèi)電磁干擾”和 “封裝外電磁輻射”也成為 2. 5D/3D 封 裝 可 靠 性 管 理 中 必 須 考 量 的問題。

目前,常規(guī)的控制封裝內(nèi)電磁干擾的方法是增加去耦電容和增加接地。2. 5D/3D 封裝中起到去耦電容作用的通常是加裝在 TSV 附近的深溝道電容器 ( deep trench capacity,DTC) 。DTC 可以屏蔽噪聲,使動態(tài)電壓變得平穩(wěn),吸收來自其他區(qū)域的電磁干擾,對 TSV 起到了良好的保護作用。但去耦電容的密度有時無法滿足抗電磁干擾和電磁輻射的需求,因此還需從設(shè)計的角度來減少電磁干擾和電磁輻射。

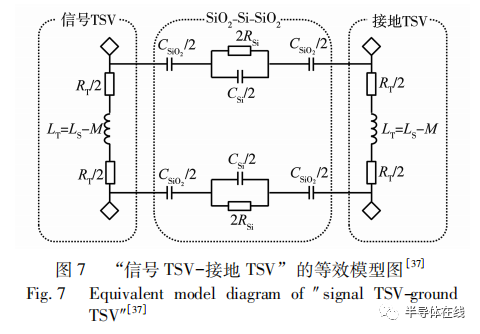

在 2. 5D/3D 封裝內(nèi)部,流過信號 TSV 的電流會將電磁波引入具有半導(dǎo)體特性的 Si 襯底中,這些電磁波會引起 Si 襯底中載流子的運動及濃度的變化,從而對周圍的有源器件和其他 TSV ( 如接地TSV) 產(chǎn)生電磁干擾,這就是 “封裝內(nèi)電磁干擾”。以信號 TSV 和接地 TSV 為例,二者可以構(gòu)成金屬-絕緣體-半導(dǎo)體-絕緣體-金屬結(jié)構(gòu),且二者的電流方向相反。其等效的模型圖如圖 7 所示。圖中:RT和 RSi分別為 TSV 和 Si 襯底的電阻; LT和 LS分別為 TSV 和串聯(lián)時等效的自感; M 為兩個 TSV 之間的互感; CSi和 CSiO2分別為 Si 襯底和 SiO2絕緣層的電容。當(dāng)通過低頻電流時,電容起主導(dǎo)作用,因此決定信號傳輸速率的因素為兩個 SiO2層的厚度及節(jié)距,當(dāng) SiO2 層的厚度較薄、節(jié)距較大時,電容增大,會導(dǎo)致嚴(yán)重的信號損耗。當(dāng)電流頻率逐漸增高時,電感逐漸成為主導(dǎo)因素,通孔高度、孔徑及節(jié)距等將對電感產(chǎn)生影響。各種寄生電阻、電容和電感是 TSV 之間產(chǎn)生電磁干擾的來源。在低頻段( <1 GHz) 時,電磁干擾會隨著絕緣層厚度的增加而減小; 在中頻段 ( 1 ~ 10 GHz) 時,電磁干擾會隨 著 通 孔 的 孔 徑 增 加 而 增 大; 在 高 頻 段( >10 GHz) 時,通孔孔徑對電磁干擾的影響減小,通孔高度和節(jié)距的影響增大,電磁干擾會隨著高度和節(jié)距的增加而增大。因此,對于不同工作頻率下的 2. 5D/3D 封裝芯片的 TSV,調(diào)節(jié)相對應(yīng)的影響較大的參數(shù)可以從設(shè)計上減小封裝內(nèi)電磁干擾的程度。

封裝外電磁輻射主要由系統(tǒng)內(nèi)部的電流產(chǎn)生,從芯片設(shè)計上較難減少系統(tǒng)向外的電磁輻射,目前工業(yè)上采取的辦法是涂覆金屬屏蔽層。電磁輻射接觸金屬表面時,大部分電磁輻射會被反射,未被反射的電磁輻射會在金屬材料中產(chǎn)生渦流轉(zhuǎn)化為熱能被消耗掉,另外,金屬中的電子還會發(fā)生電磁感應(yīng),產(chǎn)生反向的電磁場,抵消一部分電磁輻射。在涂覆了金屬屏蔽層后,絕大多數(shù)向外的電磁輻射都會被消耗,達到可靠性標(biāo)準(zhǔn)。

5 結(jié)語

本文對晶圓級多層堆疊技術(shù)的兩項關(guān)鍵工藝———TSV 工藝和晶圓鍵合與解鍵合工藝進行了系統(tǒng)的介紹,對工藝過程中各項過程的實現(xiàn)方式進行了多方位的對比,并對晶圓級多層堆疊技術(shù)在2. 5D/3D 封裝中的可靠性管理進行了分析。

采用無凸點的方法進行晶圓到晶圓 ( W2W)的鍵合對芯片的良率要求較高。除此之外,無間隙鍵合的兩片晶圓/芯片也對堆疊芯片的熱管理以及鍵合環(huán)境等提出了更高的要求。將無凸點的方法應(yīng)用于晶圓級多層堆疊技術(shù)的產(chǎn)業(yè)化之前,降低成本、優(yōu)化設(shè)計和工藝參數(shù)、W2W 鍵合對準(zhǔn)、晶圓翹曲等方面仍有大量的研究工作需要進行。

當(dāng)前,晶圓級多層堆疊技術(shù)在工業(yè)中主流的產(chǎn)業(yè)化方向是利用 TSV 和微凸點技術(shù)將芯片堆疊起來,但無凸點工藝是一條更加有效的道路,其具有更好的電性能、更低的功耗,能制造出更輕薄的堆疊芯片,將會是未來三維堆疊芯片的主流發(fā)展方向。

來源: 趨勢與展望

作者:鄭凱/周亦康/高穎/張昕(北方集成電路技術(shù)創(chuàng)新中心 ( 北京) 有限公司),

宋昌明(清華大學(xué)),蔡堅(清華大學(xué) ,北京信息科學(xué)與技術(shù)國家研究中心)

(以上文章系轉(zhuǎn)載,如有涉及版權(quán)等問題,請聯(lián)系我們以便處理)